Signal Integrity in High Speed Digital Circuitry

Maintaining signal integrity is a critical challenge in modern electronics, where high-speed data transmission requires precise engineering. As frequencies increase, designers must address physical phenomena like crosstalk, reflection, and electromagnetic interference to ensure reliable performance in complex hardware systems and advanced semiconductor devices.

The fundamental principles of electrical engineering are being pushed to their limits by the demand for faster data processing and seamless connectivity. Signal integrity refers to the quality of an electrical signal as it passes through a circuit, ensuring that the information transmitted at the source is accurately received at the destination. In high-speed digital systems, even minor physical imperfections in the transmission path can lead to significant data errors, making the study of signal behavior essential for modern hardware development.

Hardware and Circuits: Managing Signal Noise

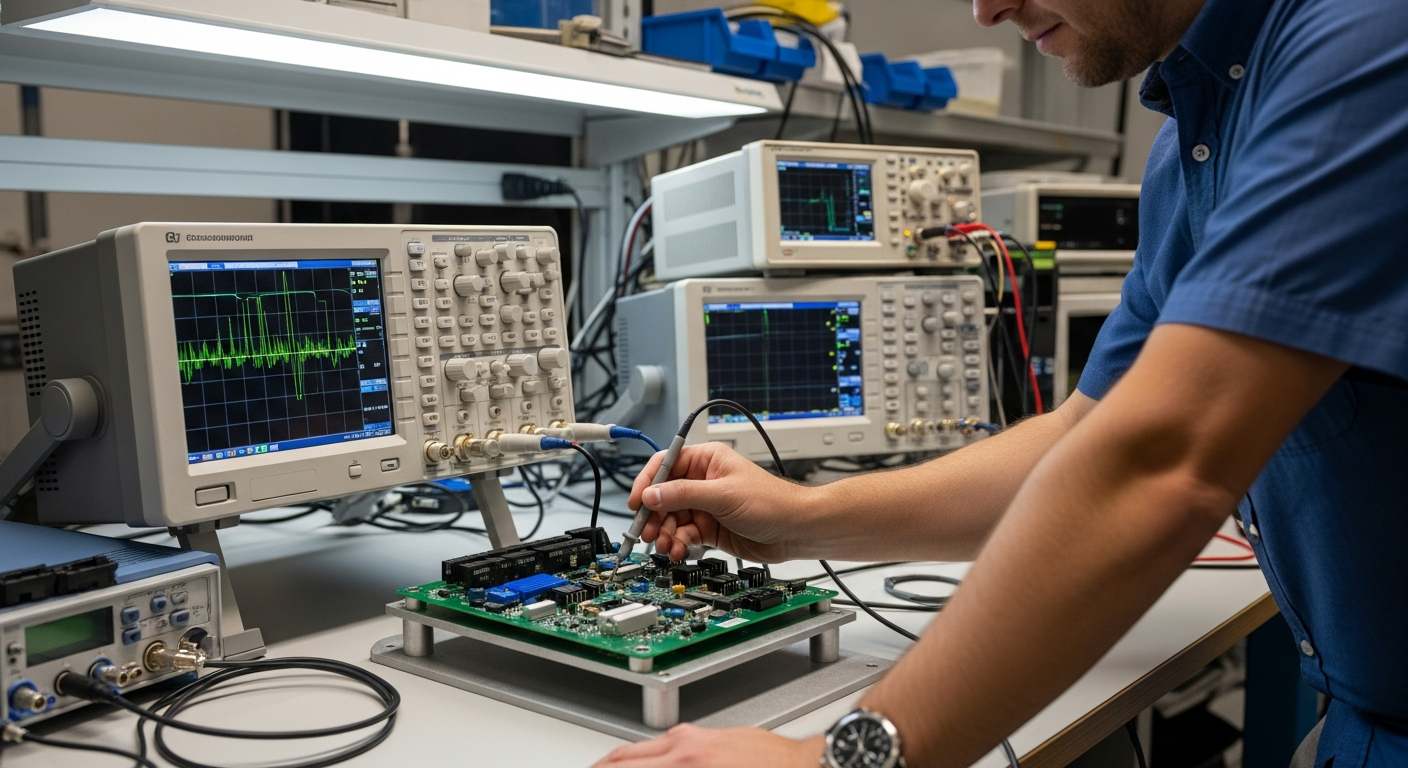

Designing robust hardware requires a deep understanding of how electrical signals behave at high frequencies. In traditional circuits, traces on a printed circuit board (PCB) are often treated as simple conductors, but in high-speed applications, they behave as transmission lines. This shift requires engineers to manage characteristic impedance to prevent signal reflections. When impedance is mismatched, a portion of the signal energy bounces back toward the source, creating interference that can distort subsequent pulses. Effective routing strategies, such as using differential pairs and maintaining consistent ground planes, are vital to preserving the clarity of the signal across the physical board layout.

Processor and Semiconductor Dynamics in Silicon

At the heart of every high-speed system is the processor, a complex semiconductor device that executes billions of operations per second. As silicon manufacturing processes shrink to the nanometer scale, the proximity of internal components increases the risk of electromagnetic coupling. This can result in crosstalk, where a signal on one path unintentionally induces a voltage on an adjacent path. Designers must implement rigorous shielding and decoupling techniques within the semiconductor architecture to isolate sensitive logic gates. Furthermore, the transition times of digital pulses in modern processors are so fast that the high-frequency components of the signal can radiate energy, turning internal traces into miniature antennas that contribute to overall system noise.

Memory and Storage Interface Reliability

The speed at which data moves between the processor and system memory is a primary bottleneck in computing performance. Modern memory technologies, such as DDR5, utilize incredibly high clock speeds that demand strict adherence to signal integrity standards. Any timing jitter—the deviation of a signal edge from its ideal position in time—can result in bit errors during the read or write process. Similarly, high-speed storage interfaces like NVMe rely on clean signals to maintain high throughput. Engineers use advanced simulation tools to model the interface between the controller and the storage medium, ensuring that the eye diagram—a visual representation of signal quality—remains open and clear of interference.

Thermal and Battery Impact on High-Speed Systems

Environmental factors such as thermal fluctuations and power delivery stability play a significant role in maintaining signal quality. High-speed components generate substantial heat, and as the temperature of the silicon and surrounding hardware rises, the electrical resistance of the traces changes. This thermal drift can alter signal timing and increase thermal noise, potentially leading to system instability. In mobile or portable devices, the battery must provide a consistent voltage even under heavy loads. Voltage sags or ripples from the power management system can translate directly into signal noise, making efficient thermal dissipation and stable battery regulation essential components of a high-performance digital design.

Implementing high-speed standards involves choosing the right interfaces for specific hardware needs. The following table compares common high-speed interface standards used in modern electronics to provide a benchmark for their capabilities.

| Interface Standard | Primary Use Case | Data Transfer Rate (Approx.) | Key Signal Integrity Feature |

|---|---|---|---|

| PCIe 5.0 | Storage and Expansion | 32 GT/s per lane | Advanced equalization and training |

| DDR5 SDRAM | System Memory | 4800 - 8400 MT/s | On-die Error Correction (ECC) |

| USB4 | Peripheral Connectivity | 40 - 80 Gbps | Multi-protocol tunneling and shielding |

| HDMI 2.1 | Display Interface | 48 Gbps | Fixed Rate Link (FRL) technology |

| Thunderbolt 4 | Universal Connectivity | 40 Gbps | Strict jitter and noise requirements |

Prices, rates, or cost estimates mentioned in this article are based on the latest available information but may change over time. Independent research is advised before making financial decisions.

Wireless and Sensor Connectivity Integration

Modern devices often integrate high-speed digital circuitry with sensitive wireless modules and sensors. The challenge lies in preventing the high-frequency noise from the digital hardware from desensitizing the wireless receiver. This is particularly difficult in compact designs where a Wi-Fi or cellular antenna is located near a high-speed processor or memory bus. Effective connectivity requires the use of specialized filters and layout isolation to ensure that the sensor data remains accurate and the wireless link remains stable. By carefully managing the electromagnetic environment, engineers can allow these disparate systems to coexist within the same silicon package or PCB without compromising performance.

Peripheral and Display Interface Standards

The final link in the signal chain often involves connecting to a peripheral device or a high-resolution display. These external interfaces must maintain signal integrity over longer distances, sometimes through cables that are several meters long. Modern display standards use sophisticated encoding schemes to pack more data into the available bandwidth while minimizing electromagnetic emissions. As peripheral demands grow, the physical connectors and cables must be engineered with high-quality shielding to protect the signals from external interference. Whether it is a high-refresh-rate monitor or an external storage array, the interface must be designed to handle the rigors of high-speed data transmission while remaining user-friendly and durable.

Ensuring signal integrity is an ongoing process that begins at the initial design phase and continues through testing and validation. As digital circuitry continues to evolve toward higher speeds and smaller form factors, the physical properties of electricity will remain a primary focus for engineers. By addressing challenges related to impedance, crosstalk, and thermal effects, the industry can continue to deliver the high-performance computing and connectivity experiences that define the modern era.